In addition, by developing the IP core for controlling the information acquisition subsystem and utilizing the inherent hardware parallel characteristics of the FPGA, the system achieves true parallel monitoring of multiple information sources, that is, while performing alpha ray detection. Acquire information such as gamma rays and temperature and humidity.

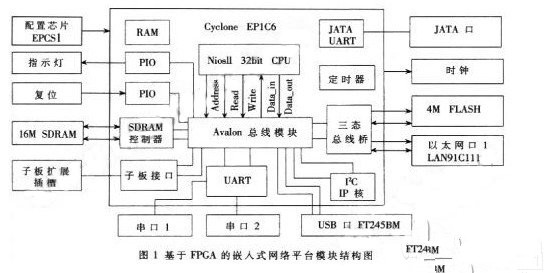

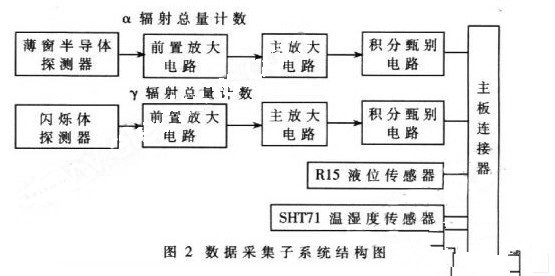

1 system hardware design and implementation <br> In the design of the system, in order to achieve versatility in hardware, the structure is divided into two parts, namely a general network platform for completing on-site monitoring and data remote transmission and for completing Environmental information acquisition subsystem for temperature and humidity, liquid level, alpha and gamma radiation measurement. The structure is shown in Figure 1 and Figure 2, respectively. The two subsystems are connected by a 40-pin flat cable. In software, considering the complexity of using the Internet for remote data transmission, the use of embedded operating systems and TCP/IP protocol stacks is an inevitable choice, so the hardware is also designed around this key point.

The Nios II soft core CPU is a general-purpose 32-bit RISC embedded processor from A137ERA. It is optimized for programmable logic and is equipped with a fully functional development kit, including C/C++ compiler and integrated development environment. (IDE), JTAG debugger, etc., are the core of ALTERA's programmable single-chip system solution.

As a soft core processor, Nios II provides configurable hardware and software debugging features, including basic JTAG run control (run, stop, single step, memory, etc.), hardware breakpoints, data triggering, on-chip and off-chip Tracking, embedded logic analyzer. These powerful tools can be used during the development phase, and can be removed after debugging and save resources. The NiosII processor also provides high, medium and low cores with different performances. It can be easily combined with more than 60 IP cores (UART, clock, DMA, SDRAM, parallel I/O, etc.) provided by ALTERA. Create a solution that is perfect for processors, peripherals, memory, and I/O interfaces for specific applications. In addition, Nios II has many other excellent features, such as instruction customization, hardware accelerators, and so on.

1.2 Network Interface Unit <br> The Ethernet interface chip uses the LAN91C111 Fast Ethernet Controller from SMSC for embedded products. The chip integrates Ethernet media access controller (MAC) and physical layer transceiver (PHY), and supports 10/100M full-duplex transmission mode, auto-negotiation and flow control. The host interface has a plurality of working modes such as a synchronous bus and an asynchronous bus, and can be conveniently connected to CPUs of various systems. In this design, the asynchronous bus interface mode is used, and the address lines and data lines are shared with the FLASH, and connected to the Avalon on-chip bus through the adaptation module on the FPGA.

1.3 Memory Units <br> Due to the need to store operating system kernel, application code, program data, etc., this system uses a FLASH chip of model AM29LV320D. The chip is introduced by AMD and has a capacity of 4MB. It supports the CFI interface. The connection with the AvMon bus requires the bus adaptation module inside the FPGA for timing matching. SDRAM is used to store the running program code and data. The HY57V563220B(L)T is a 16MB SDRAM from Hyundai. Since the chip has a port width of 32 bits, a single chip can be used in the system. SDRAM read and write timing is more complicated, and it is necessary to integrate a dedicated SDRAM controller IP core into the FPGA to interface with it.

2 Total count IP core <br> As shown in Fig. 2, the signal obtained by the α or γ detector is amplified by a linear pulse amplifier composed of two stages of amplifiers and sent to a discriminating circuit with LM393 as the core for comparison. Noise, outputting a rectangular pulse signal. For the processing of this signal, the traditional nuclear detector with MCU (microcontroller) as the core can only be realized by combining the existing hardware resources (such as timers) on the MCU with the software.

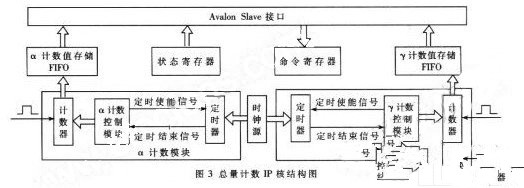

The total count IP core is part of the sub-board interface in the network platform FPGA, and its structure is shown in Figure 3. The measurement of the total amount of alpha radiation is similar to the principle of measuring the total amount of gamma radiation. The following is an example of the operation of α measurement. The clock source module generates an O by dividing the main clock. A 1 second pulse signal is used as a reference source for timer timing. The timer generates the required timing information according to the acquisition time passed from the command register.

It is worth noting that the alpha or gamma count pulse from the discriminating circuit is a signal asynchronous to the IP core operating clock, and the value of the counter is ultimately required to be stored. FIF0, therefore, the alpha or gamma count pulses are secondarily latched and shaped with the master clock, causing each asynchronous count pulse to produce a sync pulse that lasts only one master clock cycle. Counting with this pulse not only solves the problem of asynchronous signal synchronization, but also effectively filters out the interference pulse, so that the calculated value is accurate.

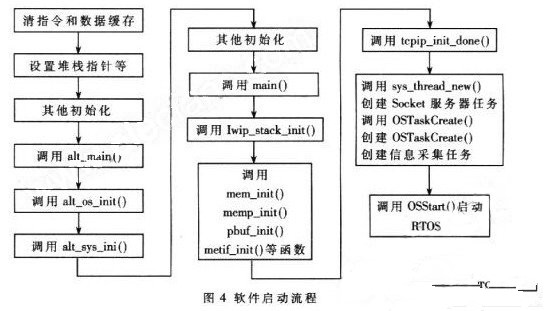

3 System Software Structure <br> In order to realize remote data transmission using Internet, the system transplants MicroC/OS2 real-time operating system and LWIP (lightweight IP protocol stack) on Nios II to develop information acquisition software on it.

3.1 Migration of MicroC/OS2 and LWIP <br> This part of the work is mainly for the specific hardware of the system to transplant and write various drivers such as temperature and humidity sensor SHT75, total count IP core, etc., so deep understanding The layer structure and details of the software are the key to successful porting.

HAL, the hardware abstraction layer, is part of the Nios II development kit, provided by ALTERA, which encapsulates the details of hardware operations in the system, and the driver is part of it. HAL abstracts six device models, including character mode devices, timer devices, file subsystems, Ethernet devices, DMA devices, and Flash devices, and provides a series of unified initialization functions and access function interfaces for each type of device. In this way, HAL provides a POSIX-like API interface to the upper layer, namely the hardware abstraction layer application programming interface.

Software development for Nios II is actually built on top of HAL, not directly to the Nios II hardware itself. The IP cores of each interface corresponding to the measurement module of this system belong to the character mode device, so the driver needs to be written according to the character mode device model in HAL.

MicroC/OS2 is a deprived real-time operating system for small, microcontrollers. It supports 56 user tasks, its kernel is preemptive, supports a variety of common inter-process communication mechanisms such as semaphores, mailboxes, message queues, etc., through which it provides the required multi-tasking environment for applications. Since MicroC/OS2 does not have a protocol stack itself, it needs to port a TCP/IP stack LWIP, thus providing a UNIX-like interface to the upper layer. LWIP supports the following network protocols: IP, ARP, ICMF, UDP, TCP. The stack requires 20KB of code storage and 4KB of data storage space, and you need to add a timer for its use when building the system.

3.2 Design of information acquisition program As a task, this module runs on the MicroC/OS2 real-time operating system and completes measurement control based on policies or remote commands for each detection subsystem. The acquired information is saved to the specified memory buffer. Zone and return the results to the remote host as required. For temperature and humidity measurement, since the humidity output of the SHT75 sensor is nonlinear, in order to obtain accurate data, the obtained data needs to be corrected according to a given formula, and the temperature output is not compensated, and the digital output is converted into The actual temperature value can be found in the SHT75 data sheet. For the processing of the total count, the module simply packs the data and hands it back to the communication server for transmission back to the remote host.

3.3 Communication Server This task is created by the sys_thread_new() function as a server* contracted port, waiting for the connection of the remote host, extracting the commands of the remote host, and sending the obtained commands to the information collection task through the message queue; The various data classifications obtained by the information collection task are sent back to the remote host as required.

LWP provides a standard Berkeley socket programming interface that provides three types of sockets, using streaming sockets, which are a connection-oriented, reliable data transfer service, meaning use The TCP protocol. Usually, the server receives a concurrent service request and activates a new process to process the client request, but for system resources and simplified design considerations, the server can only accept one connection request at a time, and this simplification is in fact Can meet the design needs.

The system uses FPGA-based system-on-chip technology and embedded system technology to realize the connection between the intelligent nuclear instrument and the Internet, and also realizes partial reconfigurability on the hardware, and can add or delete the peripheral IP core in the FPGA as needed. Achieve changes in functionality and performance of the system. At present, the system has been applied in the radioactive sample storage room, and its function and performance meet the requirements of the actual environment. Since the network platform of the system is designed as a relatively independent subsystem, it is only necessary to develop a specific detection subsystem to be applied to various corresponding fields requiring remote monitoring.

Door curtain nets have become a popular choice for homeowners seeking a practical and stylish solution to keep insects out while allowing fresh air to circulate. These nets are specifically designed to fit over doorways, providing a barrier against bugs and pests. Made from a fine mesh material, door curtain nets effectively prevent insects from entering indoor spaces, creating a comfortable and bug-free environment. They are easy to install and remove, making them a convenient option for both temporary and permanent use. With their transparent design, door curtain nets allow for unobstructed views and airflow, ensuring a pleasant and inviting entrance while keeping unwanted visitors at bay.

Door cutain net,Automatic Closing Frame Screen Door,Magnetic Insect Screen Door,Magnetic Doors Curtain

Jinwu Glass Fiber Co., Ltd , https://www.jinwuwindows.com